Xilinx ISE 14.7是一款专业的电子设计套件,也是目前的最新版本,全面支持win8和win8.1系统。Xilinx ISE为设计流程的每一步都提供了直观的生产力增强工具,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。除了功能完整,使用方便外,它的设计性能也非常好,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟布局、更好的封装和时序收敛映射,从而获得更高的设计性能,可以达到最佳的硬件设计,是FPGA的必备的设计工具。

Xilinx ISE 14.7在硬件设计上应用非常广泛,覆盖从系统级设计探索、软件开发和基于HDL硬件设计,直到验证、调试和PCB设计集成的全部设计流程。运行速度非常的快,设计人员可以在一天时间里完成多次设计反复,这一增强设计环境现在还提供了SmartXplorer技术。专门为解决设计人员所面临的时序收敛和生产力这两大艰巨挑战而开发,支持在多台Linux主机上进行分布式处理,可在一天时间里完成更多次实施过程。通过利用分布式处理和多种实施策略,性能可以提升多达38%。SmartXplorer技术同时还提供了一些工具,允许用户利用独立的时序报告监控每个运行实例。

功能特色

ISE的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了可编程逻辑器件开发的全过程,从功能上讲,完成CPLD/FPGA的设计流程无需借助任何第三方EDA软件。

1、图形或文本输入(Design Entry)

图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试激励生成器(HDL Bencher)等。

常用的设计输入方法是硬件描述语言(HDL)和原理图设计输入方法。原理图输入是一种常用的基本的输入方法,其是利用元件库的图形符号和连接线在ISE软件的图形编辑器中作出设计原理图,ISE中设置了具有各种电路元件的元件库,包括各种门电路、触发器、锁存器、计数器、各种中规模电路、各种功能较强的宏功能块等用户只要点击这些器件就能调入图形编辑器中。这种方法的优点是直观、便于理解、元件库资源丰富。但是在大型设计中,这种方法的可维护性差,不利于模块建设与重用。更主要的缺点是:当所选用芯片升级换代后,所有的原理图都要作相应的改动。故在ISE软件中一般不利用此种方法。

为了克服原理图输入方法的缺点,目前在大型工程设计中,在ISE软件中常用的设计方法是HDL设计输入法,其中影响最为广泛的HDL语言是VHDL和Verilog HDL。它们的共同优点是利于由顶向下设计,利于模块的划分与复用,可移植性好,通用性强,设计不因芯片的工艺和结构的变化而变化,更利于向ASIC的移植,故在ISE软件中推荐使用HDL设计输入法。

波形输入及状态机输入方法是两种最常用的辅助设计输入方法,使用波形输入法时,只要绘制出激励波形的输出波形,ISE软件就能自动地根据响应关系进行设计;而使用状态机输入时,只需设计者画出状态转移图,ISE软件就能生成相应的HDL代码或者原理图,使用十分方便。其中ISE工具包中的StateCAD就能完成状态机输入的功能。但是需要指出的是,后两种设计方法只能在某些特殊情况下缓解设计者的工作量,并不适合所有的设计。

2、综合(Synthesis)

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

在Xilinx ISE中,综合工具主要有Synplicity公司的Synplify/Synplify Pro,Synopsys公司的FPGA Compiler II/ Express, Exemplar Logic公司的LeonardoSpectrum和Xilinx ISE中的XST等,它们是指将HDL语言、原理图等设计输入翻译成由与、或、非门,RAM,寄存器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求优化所形成的逻辑连接,输出edf和edn等文件,供CPLD/FPGA厂家的布局布线器进行实现。

3、实现(Implementation)

实现是根据所选的芯片的型号将综合输出的逻辑网表适配到具体器件上。Xilinx ISE的实现过程分为:翻译(Translate)、映射(Map)、布局布线(Place Route)等3个步骤。

ISE集成的实现工具主要有约束编辑器(Constraints Editor)、引脚与区域约束编辑器(PACE)、时序分析器(Timing Analyzer)、FPGA底层编辑器(FGPA Editor)、芯片观察窗(Chip Viewer)和布局规划器(Floorplanner)等。

4、验证(Verification)

验证(Verification)包含综合后仿真和功能仿真(Simulation)等。功能仿真就是对设计电路的逻辑功能进行模拟测试,看其是否满足设计要求,通常是通过波形图直观地显示输入信号与输出信号之间的关系。 综合后仿真在针对目标器件进行适配之后进行,综合后仿真接近真实器件的特性进行,能精确给出输入与输出之间的信号延时数据。

ISE可结合第三方软件进行仿真,常用的工具如Model Tech公司的仿真工具ModelSim和测试激励生成器HDL Bencher ,Synopsys公司的VCS等。通过仿真能及时发现设计中的错误,加快设计中的错误,加快设计进度,提高设计的可靠性。

每个仿真步骤如果出现问题,就需要根据错误的定位返回到相应的步骤更改或者重新设计。

5、下载

下载(Download)即编程(Program)设计开发的最后步骤就是将已经仿真实现的程序下载到开发板上,进行在线调试或者说将生成的配置文件写入芯片中进行测试。在ISE中对应的工具是iMPACT。

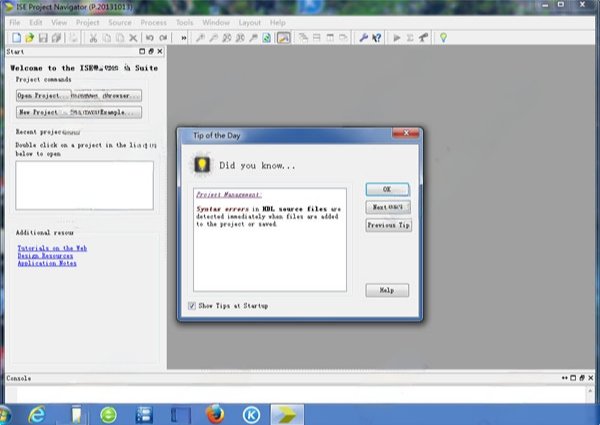

Xilinx ISE14.7安装教程

1、我们先解压文件,得到下载的网盘,下载完了后点击xsetup,exe文件

2、等待载入并弹出安装欢迎界面,点击NEXT

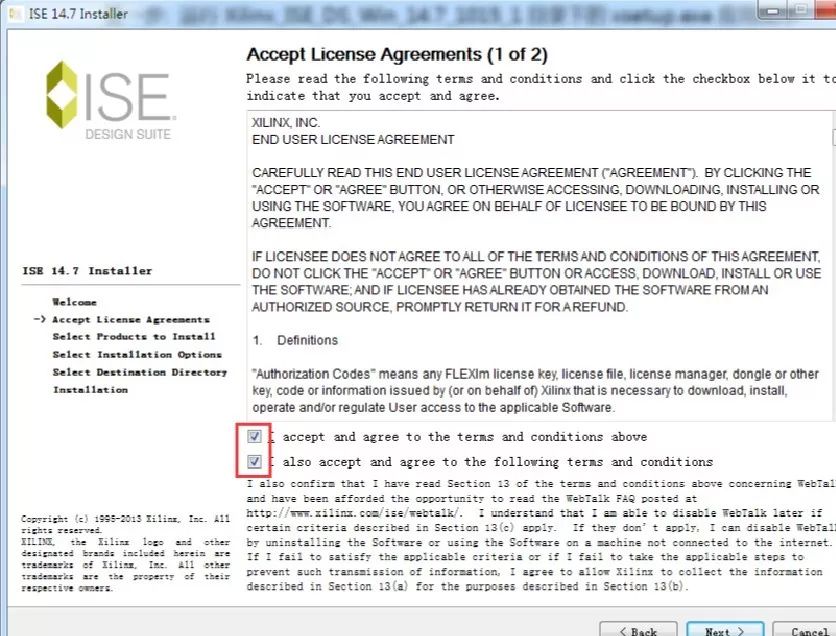

3、勾选允许用户协议,点击NEXT

4、同样必须接受许可

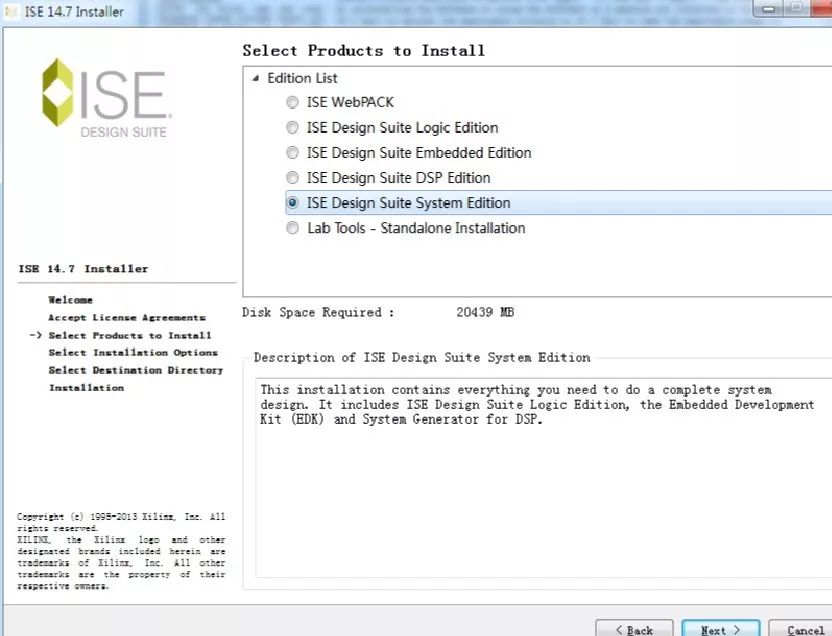

5、选择要安装的软件类型,根据大家需求进行选择,这里选“ISE Design Suite System Edition”

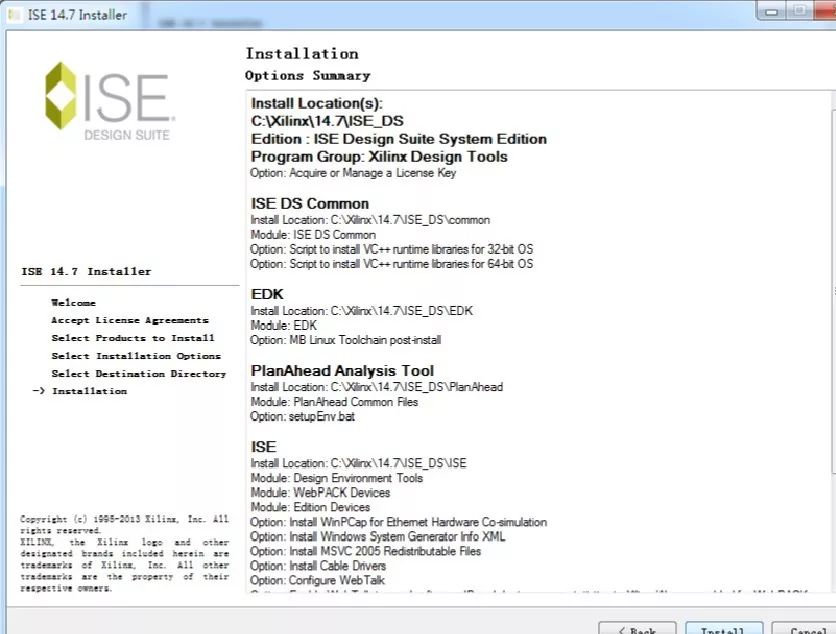

6、选择安装路径,根据大家磁盘情况进行设置,这里为C盘,Next~~

7、点击NEXT

8、确认安装信息后,点击Install开始安装

9、安装期间会跳出以下MATLAB安装的对话框,点击Ok就可以

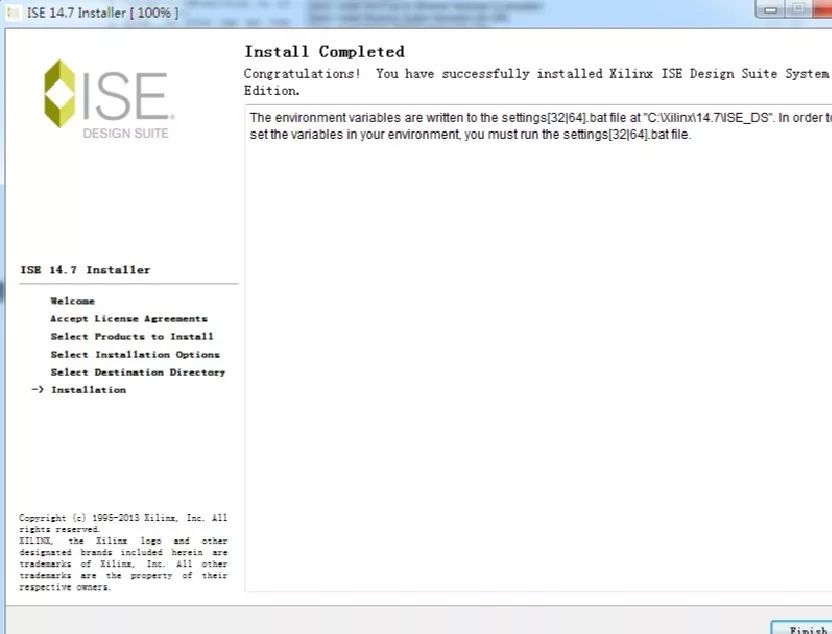

10、现在就安装好了,现在我们点击Finish

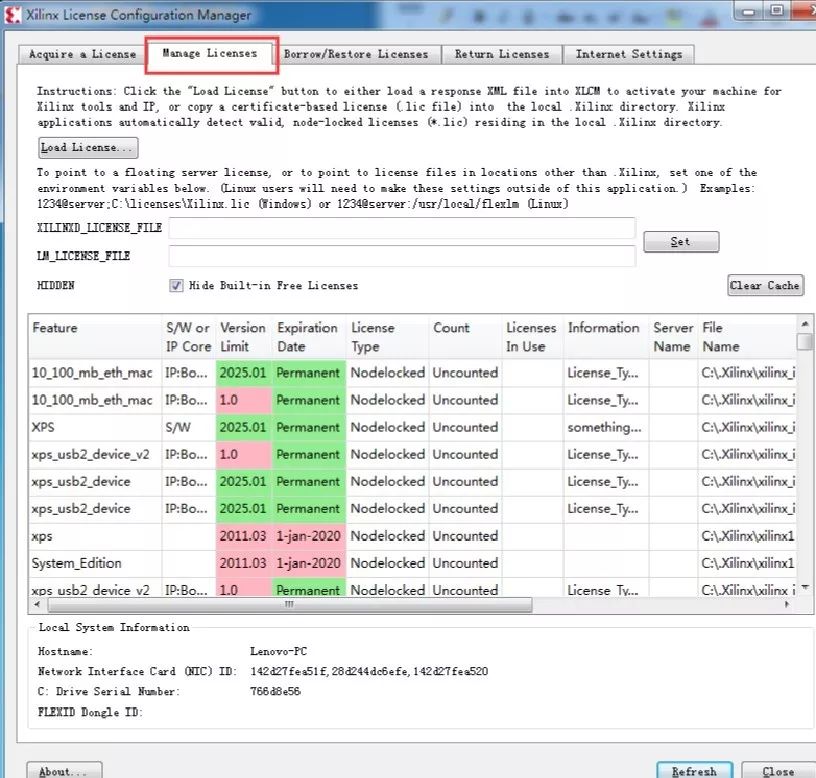

11、在弹出的Xilinx LicenseConfiguration Manager里点击Manage Licenses按钮。

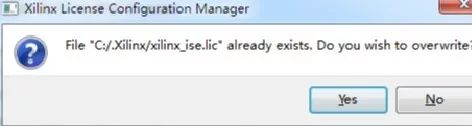

12、如果弹出Xilinx ise.lic文件已经存在的对话框点击Yes覆盖

13、这个时候会提示安装成功,至此软件就算成功安装完成了

发表评论

11人参与,11条评论- 第11楼北京市网友发表于: 2024-02-29 23:14:58

- good0盖楼(回复)

- 第10楼内蒙古呼和浩特市联通网友发表于: 2021-03-06 17:11:18

- 不错的软件0盖楼(回复)

- 第9楼江苏省宿迁市移动网友发表于: 2020-02-04 20:06:56

- 好东西0盖楼(回复)

- 第8楼湖北省孝感市移动网友发表于: 2019-11-14 21:50:23

- good0盖楼(回复)

- 第7楼湖北省武汉市华中科技大学东校区网友发表于: 2019-11-08 12:02:32

- 不错不错很好很好很棒很棒0盖楼(回复)

- 第6楼天津市红桥区联通网友发表于: 2019-10-30 17:47:11

- 很不错哦0盖楼(回复)

- 第5楼四川省成都市电信网友发表于: 2019-10-29 18:26:50

- 顶顶顶0盖楼(回复)

- 第4楼陕西省西安市电信网友发表于: 2019-10-27 21:20:36

- 好好好0盖楼(回复)

- 第3楼浙江省杭州市电信网友发表于: 2019-10-17 14:50:57

- 免费就是好0盖楼(回复)

- 第2楼四川省绵阳市移动网友发表于: 2019-04-10 10:33:00

- 谢谢,感谢0盖楼(回复)

- 第1楼浙江省杭州市移动网友发表于: 2019-02-28 16:22:23

- 好的哼0盖楼(回复)

软件排行榜

热门推荐

modbus poll官方版 v12.1.1 32位/64位2.05M / 多国语言

modbus poll官方版 v12.1.1 32位/64位2.05M / 多国语言 睿达RDWorks激光雕刻切割软件 v8.01.68官方版187.88M / 简体中文

睿达RDWorks激光雕刻切割软件 v8.01.68官方版187.88M / 简体中文 cam350 10.7中文版 附安装教程218.79M / 简体中文

cam350 10.7中文版 附安装教程218.79M / 简体中文 proteus8.16安装包 636.87M / 简体中文

proteus8.16安装包 636.87M / 简体中文 ANSYS Products 2023官方版 R123.2G / 英文

ANSYS Products 2023官方版 R123.2G / 英文 Multisim14.3官方版 877.71M / 简体中文

Multisim14.3官方版 877.71M / 简体中文 altium designer 16中文激活版 v16.1.12完整版3.15G / 多国语言[中文]

altium designer 16中文激活版 v16.1.12完整版3.15G / 多国语言[中文] FluidSIM中文版 v3.632.21M / 简体中文

FluidSIM中文版 v3.632.21M / 简体中文 电缆选型专家电脑版 v3.03官方版4.99M / 简体中文

电缆选型专家电脑版 v3.03官方版4.99M / 简体中文

modbus poll官方版 v12.1.1 32位/64位

modbus poll官方版 v12.1.1 32位/64位 睿达RDWorks激光雕刻切割软件 v8.01.68官方版

睿达RDWorks激光雕刻切割软件 v8.01.68官方版 cam350 10.7中文版 附安装教程

cam350 10.7中文版 附安装教程 proteus8.16安装包

proteus8.16安装包  ANSYS Products 2023官方版 R1

ANSYS Products 2023官方版 R1 Multisim14.3官方版

Multisim14.3官方版  altium designer 16中文激活版 v16.1.12完整版

altium designer 16中文激活版 v16.1.12完整版 FluidSIM中文版 v3.6

FluidSIM中文版 v3.6 电缆选型专家电脑版 v3.03官方版

电缆选型专家电脑版 v3.03官方版 赣公网安备36010602000168号

赣公网安备36010602000168号